4.7/5 - (3 votes)

[wpbread]

UVM(Universal Verification Methodology) is a standard methodology for verifying digital designs, primarily using the SystemVerilog language. It provides a library of base classes that can be used to build testbenches and test environments for verifying digital designs(DUT).

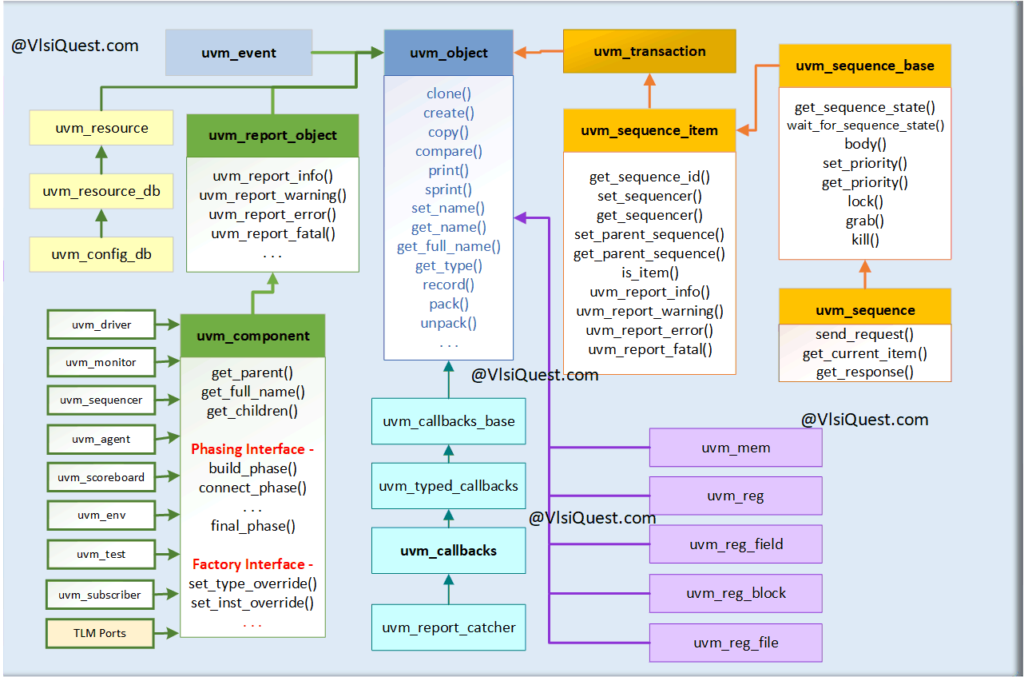

The UVM class hierarchy looks like-

UVM is an open source code that provides:

- A library of base classes for building testbench components.

- A factory for constructing objects and substituting objects.

- Verification phases for synchronizing concurrent processes.

- A reporting mechanism for a consistent way of printing and logging results.

- Transaction Level Modeling (TLM) for communication between verification components.

- Macros to semi-automate generation of required UVM code.

The UVM base classes include:

uvm_object: This is the base class for all UVM data classes. It provides basic functionality for cloning, comparing, and printing UVM objects.

uvm_component: This is the base class for all UVM components. It provides a framework for building hierarchical testbenches and test environments.

uvm_test: This is the base class for all UVM test cases. It provides a framework for defining and running test cases.

uvm_sequence_item: This is the base class for all UVM sequence items. It provides a framework for defining and generating stimulus.

uvm_sequence: This is the base class for all UVM sequences. It provides a framework for defining and controlling the execution of sequences.

uvm_driver: This is the base class for all UVM drivers. It provides a framework for driving stimulus to the design.

uvm_monitor: This is the base class for all UVM monitors. It provides a framework for monitoring the behavior of the design.

uvm_scoreboard: This is the base class for all UVM scoreboards. It provides a framework for checking the correctness of the design’s output.

These base classes form the foundation of the UVM methodology and can be extended and customized to create more complex testbenches and test environments.